ଉଚ୍ଚ-ଶକ୍ତି ପଲ୍ସଡ୍ ଲେଜରସମ୍ପୂର୍ଣ୍ଣ ଫାଇବର MOPA ସଂରଚନା ସହିତ

ଫାଇବର ଲେଜରର ମୁଖ୍ୟ ଗଠନମୂଳକ ପ୍ରକାରଗୁଡ଼ିକ ମଧ୍ୟରେ ସିଙ୍ଗଲ୍ ରେଜୋନେଟର, ବିମ୍ କମ୍ବିନେସନ୍ ଏବଂ ମାଷ୍ଟର୍ ଓସିଲେଟିଂ ପାୱାର ଆମ୍ପ୍ଲିଫାୟର (MOPA) ଗଠନ ଅନ୍ତର୍ଭୁକ୍ତ। ସେମାନଙ୍କ ମଧ୍ୟରେ, ଉଚ୍ଚ-କାର୍ଯ୍ୟଦକ୍ଷତା ହାସଲ କରିବାର କ୍ଷମତା ଯୋଗୁଁ MOPA ଗଠନ ବର୍ତ୍ତମାନର ଗବେଷଣାର ଆକର୍ଷଣୀୟ ସ୍ଥାନ ମଧ୍ୟରୁ ଗୋଟିଏ ପାଲଟିଛି।ସ୍ପନ୍ଦିତ ଲେଜରଆଡଜଷ୍ଟେବଲ୍ ପଲ୍ସ ପ୍ରସ୍ଥ ଏବଂ ପୁନରାବୃତ୍ତି ଆବୃତ୍ତି ସହିତ ଆଉଟପୁଟ୍ (ପଲ୍ସ ପ୍ରସ୍ଥ ଏବଂ ପୁନରାବୃତ୍ତି ଆବୃତ୍ତି ଭାବରେ ଜଣାଶୁଣା)।

MOPA ଲେଜରର କାର୍ଯ୍ୟ ନୀତି ନିମ୍ନଲିଖିତ: ମୁଖ୍ୟ ଓସିଲେଟର (MO) ଏକ ଉଚ୍ଚ-କ୍ଷମତା ସମ୍ପନ୍ନ ବିହନ ଉତ୍ସଅର୍ଦ୍ଧପରିବାହୀ ଲେଜରଯାହା ସିଧାସଳଖ ପଲ୍ସ ମଡ୍ୟୁଲେସନ୍ ମାଧ୍ୟମରେ ଆଡଜଷ୍ଟେବଲ୍ ପାରାମିଟର ସହିତ ବୀଜ ସଙ୍କେତ ଆଲୋକ ସୃଷ୍ଟି କରେ। କ୍ଷେତ୍ର ପ୍ରୋଗ୍ରାମେବଲ୍ ଗେଟ୍ ଆରେ (FPGA) ମୁଖ୍ୟ ନିୟନ୍ତ୍ରଣ ଆଡଜଷ୍ଟେବଲ୍ ପାରାମିଟର ସହିତ ପଲ୍ସ କରେଣ୍ଟ ସଙ୍କେତ ବାହାର କରେ, ଯାହା ଡ୍ରାଇଭ୍ ସର୍କିଟ୍ ଦ୍ୱାରା ବିହନ ଉତ୍ସକୁ ପରିଚାଳନା କରିବା ଏବଂ ବୀଜ ଆଲୋକର ପ୍ରାରମ୍ଭିକ ମଡ୍ୟୁଲେସନ୍ ସମାପ୍ତ କରିବା ପାଇଁ ନିୟନ୍ତ୍ରିତ ହୁଏ। FPGA ମୁଖ୍ୟ ନିୟନ୍ତ୍ରଣ ବୋର୍ଡରୁ ନିୟନ୍ତ୍ରଣ ନିର୍ଦ୍ଦେଶ ପାଇବା ପରେ, ପମ୍ପ ଉତ୍ସ ଡ୍ରାଇଭ୍ ସର୍କିଟ୍ ପମ୍ପ ଆଲୋକ ସୃଷ୍ଟି କରିବା ପାଇଁ ପମ୍ପ ଉତ୍ସ ଆରମ୍ଭ କରେ। ବିମ୍ ସ୍ପ୍ଲିଟର୍ ଦ୍ୱାରା ବୀଜ ଆଲୋକ ଏବଂ ପମ୍ପ ଆଲୋକ ଯୋଡ଼ି ହେବା ପରେ, ସେମାନଙ୍କୁ ଯଥାକ୍ରମେ ଦୁଇ-ସ୍ତରୀୟ ଅପ୍ଟିକାଲ୍ ଆମ୍ପ୍ଲିଫିକେସନ୍ ମଡ୍ୟୁଲ୍ରେ Yb3+ -ଡୋପ୍ ଡବଲ୍-କ୍ଲାଡ୍ ଅପ୍ଟିକାଲ୍ ଫାଇବର (YDDCF) ରେ ଇଞ୍ଜେକ୍ଟ କରାଯାଏ। ଏହି ପ୍ରକ୍ରିୟା ସମୟରେ, Yb3+ ଆୟନ୍ ପମ୍ପ ଆଲୋକର ଶକ୍ତିକୁ ଶୋଷଣ କରି ଏକ ଜନସଂଖ୍ୟା ବିପରୀତ ବଣ୍ଟନ ଗଠନ କରେ। ପରବର୍ତ୍ତୀ ସମୟରେ, ଯାତ୍ରା ତରଙ୍ଗ ପ୍ରବର୍ଦ୍ଧନ ଏବଂ ଉତ୍ତେଜିତ ନିର୍ଗମନର ନୀତି ଉପରେ ଆଧାରିତ, ବୀଜ ସଙ୍କେତ ଆଲୋକ ଦୁଇ-ସ୍ତରୀୟ ଅପ୍ଟିକାଲ୍ ଆମ୍ପ୍ଲିଫିକେସନ୍ ମଡ୍ୟୁଲ୍ରେ ଉଚ୍ଚ ଶକ୍ତି ଲାଭ ହାସଲ କରେ, ଶେଷରେ ଏକ ଉଚ୍ଚ-ଶକ୍ତି ବାହାର କରେ।ନାନୋସେକେଣ୍ଡ ପଲ୍ସଡ୍ ଲେଜର। ସର୍ବାଧିକ ଶକ୍ତି ବୃଦ୍ଧି ହେତୁ, ଲାଭ କ୍ଲାମ୍ପିଂ ପ୍ରଭାବ ହେତୁ ପରିବର୍ଦ୍ଧିତ ପଲ୍ସ ସିଗନାଲ ପଲ୍ସ ପ୍ରସ୍ଥ ସଙ୍କୋଚନ ଅନୁଭବ କରିପାରେ। ବ୍ୟବହାରିକ ପ୍ରୟୋଗରେ, ଆଉଟପୁଟ୍ ଶକ୍ତିକୁ ଆହୁରି ବୃଦ୍ଧି କରିବା ଏବଂ ଦକ୍ଷତା ହାସଲ କରିବା ପାଇଁ ବହୁ-ସ୍ତରୀୟ ପ୍ରବର୍ଦ୍ଧନ ଗଠନ ପ୍ରାୟତଃ ଗ୍ରହଣ କରାଯାଏ।

MOPA ଲେଜର ସର୍କିଟ୍ ସିଷ୍ଟମ୍ ଏକ FPGA ମୁଖ୍ୟ ନିୟନ୍ତ୍ରଣ ବୋର୍ଡ, ଏକ ପମ୍ପ ଉତ୍ସ, ଏକ ବିହନ ଉତ୍ସ, ଏକ ଡ୍ରାଇଭର ସର୍କିଟ୍ ବୋର୍ଡ, ଏକ ଆମ୍ପ୍ଲିଫାୟର, ଇତ୍ୟାଦିକୁ ନେଇ ଗଠିତ। FPGA ମୁଖ୍ୟ ନିୟନ୍ତ୍ରଣ ବୋର୍ଡ ବିହନ ଉତ୍ସକୁ MW-ସ୍ତରୀୟ କଞ୍ଚା ବୀଜ ଆଲୋକ ପଲ୍ସକୁ ଆଡଜଷ୍ଟେବଲ୍ ପାରାମିଟର ସହିତ ଆଉଟପୁଟ୍ କରିବାକୁ ଚାଳିତ କରେ ଯାହା ଆଡଜଷ୍ଟେବଲ୍ ତରଙ୍ଗ, ପଲ୍ସ ପ୍ରସ୍ଥ (5 ରୁ 200ns), ଏବଂ ପୁନରାବୃତ୍ତି ହାର (30 ରୁ 900kHz) ସହିତ ପଲ୍ସ ବୈଦ୍ୟୁତିକ ସଙ୍କେତ ସୃଷ୍ଟି କରିଥାଏ। ଏହି ସଙ୍କେତ ପ୍ରିଆମ୍ପ୍ଲିଫାୟର ଏବଂ ମୁଖ୍ୟ ଆମ୍ପ୍ଲିଫାୟର ଦ୍ୱାରା ଗଠିତ ଦୁଇ-ଷ୍ଟେଜ୍ ଅପ୍ଟିକାଲ୍ ଆମ୍ପ୍ଲିଫିକେସନ୍ ମଡ୍ୟୁଲ୍ କୁ ଆଇସୋଲେଟର ମାଧ୍ୟମରେ ଇନପୁଟ୍ କରାଯାଏ, ଏବଂ ଶେଷରେ କୋଲିମେସନ୍ ଫଙ୍କସନ୍ ସହିତ ଅପ୍ଟିକାଲ୍ ଆଇସୋଲେଟର ମାଧ୍ୟମରେ ଉଚ୍ଚ-ଶକ୍ତି ସର୍ଟ-ପଲ୍ସ ଲେଜର ଆଉଟପୁଟ୍ କରେ। ବୀଜ ଉତ୍ସ ଏକ ଆଭ୍ୟନ୍ତରୀଣ ଫଟୋଡିଟେକ୍ଟର ସହିତ ସଜ୍ଜିତ ଯାହା ପ୍ରକୃତ ସମୟରେ ଆଉଟପୁଟ୍ ଶକ୍ତି ନିରୀକ୍ଷଣ କରେ ଏବଂ ଏହାକୁ FPGA ମୁଖ୍ୟ ନିୟନ୍ତ୍ରଣ ବୋର୍ଡକୁ ଫେରାଇ ଆଣେ। ମୁଖ୍ୟ ନିୟନ୍ତ୍ରଣ ବୋର୍ଡ ପମ୍ପ ଉତ୍ସ 1, 2 ଏବଂ 3 ର ଖୋଲିବା ଏବଂ ବନ୍ଦ କରିବା କାର୍ଯ୍ୟ ହାସଲ କରିବା ପାଇଁ ପମ୍ପ ଡ୍ରାଇଭ୍ ସର୍କିଟ୍ 1 ଏବଂ 2 କୁ ନିୟନ୍ତ୍ରଣ କରେ। ଯେତେବେଳେଫଟୋଡିଟେକ୍ଟରସିଗନାଲ ଲାଇଟ୍ ଆଉଟପୁଟ୍ ଚିହ୍ନଟ କରିବାରେ ବିଫଳ ହେଲେ, ସିଡ୍ ଲାଇଟ୍ ଇନପୁଟ୍ ଅଭାବରୁ YDDCF ଏବଂ ଅପ୍ଟିକାଲ୍ ଡିଭାଇସଗୁଡ଼ିକୁ କ୍ଷତି ନ କରିବା ପାଇଁ ମୁଖ୍ୟ ନିୟନ୍ତ୍ରଣ ବୋର୍ଡ ପମ୍ପ ଉତ୍ସକୁ ବନ୍ଦ କରିଦେବ।

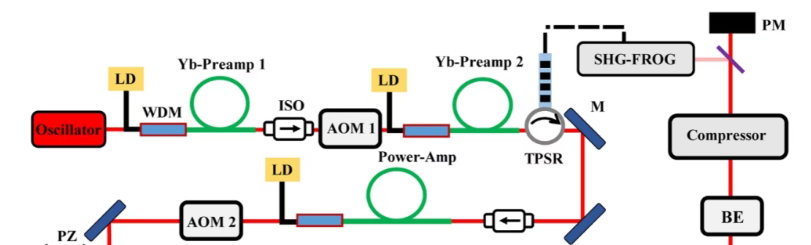

MOPA ଲେଜର ଅପ୍ଟିକାଲ୍ ପଥ ସିଷ୍ଟମ୍ ଏକ ସମ୍ପୂର୍ଣ୍ଣ ଫାଇବର ଗଠନ ଗ୍ରହଣ କରେ ଏବଂ ଏଥିରେ ଏକ ମୁଖ୍ୟ ଦୋଳନ ମଡ୍ୟୁଲ୍ ଏବଂ ଏକ ଦୁଇ-ସ୍ତରୀୟ ଆମ୍ପ୍ଲିଫିକେସନ୍ ମଡ୍ୟୁଲ୍ ରହିଥାଏ। ମୁଖ୍ୟ ଦୋଳନ ମଡ୍ୟୁଲ୍ ଏକ ସେମିକଣ୍ଡକ୍ଟର ଲେଜର ଡାଏଡ୍ (LD) ଯାହାର କେନ୍ଦ୍ରୀୟ ତରଙ୍ଗଦୈର୍ଘ୍ୟ 1064nm, 3nm ରେଖାପ୍ରସ୍ଥ ଏବଂ ସର୍ବାଧିକ ନିରନ୍ତର ଆଉଟପୁଟ୍ ଶକ୍ତି 400mW ବୀଜ ଉତ୍ସ ଭାବରେ ଗ୍ରହଣ କରେ, ଏବଂ ଏହାକୁ 99%@1063.94nm ପ୍ରତିଫଳନ ଏବଂ 3.5nm ରେଖାପ୍ରସ୍ଥ ସହିତ ଏକ ଫାଇବର ବ୍ରାଗ୍ ଗ୍ରେଟିଂ (FBG) ସହିତ ମିଶ୍ରଣ କରି ଏକ ତରଙ୍ଗଦୈର୍ଘ୍ୟ ଚୟନ ପ୍ରଣାଳୀ ଗଠନ କରେ। 2-ସ୍ତରୀୟ ଆମ୍ପ୍ଲିଫିକେସନ୍ ମଡ୍ୟୁଲ୍ ଏକ ବିପରୀତ ପମ୍ପ ଡିଜାଇନ୍ ଗ୍ରହଣ କରେ, ଏବଂ 8 ଏବଂ 30μm କୋର୍ ବ୍ୟାସ ସହିତ YDDCF ଯଥାକ୍ରମେ ଲାଭ ଗଣମାଧ୍ୟମ ଭାବରେ ବିନ୍ୟାସିତ ହୁଏ। ଅନୁରୂପ ଆବରଣ ପମ୍ପ ଅବଶୋଷଣ ଗୁଣାଙ୍କ ଯଥାକ୍ରମେ 1.0 ଏବଂ 2.1dB/m@915nm ଅଟେ।

ପୋଷ୍ଟ ସମୟ: ସେପ୍ଟେମ୍ବର-୧୭-୨୦୨୫